Shriram Subramanian, Raghavendra Barkur, Joshua P, Shanthibhushan B

ABB Global Industries and Services Private Limited, India

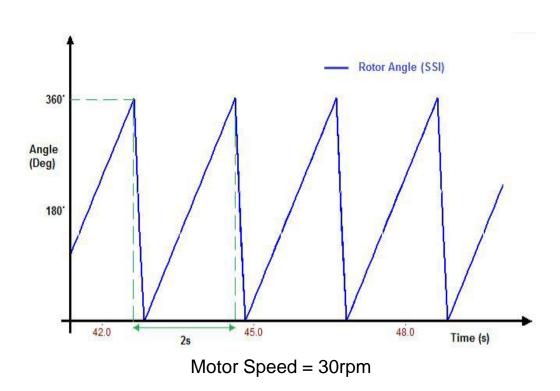

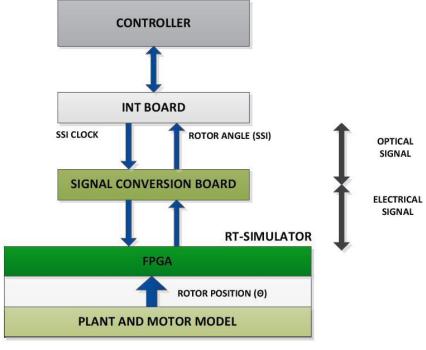

Objective: SSI protocol implementation in FPGA layer of a Real time Simulator

Need: Limitation of DO, Encoder hardware elimination

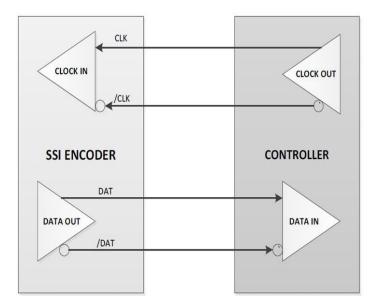

Basic Synchronous Serial Interface Communication

HiL Setup

Implementation:

$$timeout\ counter = \frac{{\scriptstyle INT\ board\ clock\ period - (Max\ resolution*pulse\ period)}}{{\scriptstyle FPGA\ clock\ period}}$$

| Clock Rising Edge | Clock Falling Edge | Counter value                            | Transmitted Data              |

|-------------------|--------------------|------------------------------------------|-------------------------------|

| 0/1               | 0                  | 0                                        | Load Parallel Data            |

| 0                 | 1                  | Set to 2000                              | Send the last transmitted bit |

| 1                 | 0                  | 0 <counter<br>Value&lt;2000</counter<br> | Send the next bit             |

| 0                 | 0                  | 0 <counter<br>Value&lt;2000</counter<br> | Send the last transmitted bit |

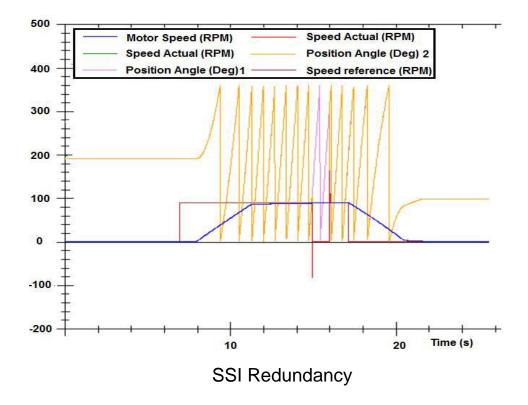

Redundancy: Two separate Clock pulse is received and two separate serial data are sent out

#### Results: